📚 What is an Interrupt?

In simple terms, an interrupt in 8085 is a signal that temporarily pauses the main program and redirects the CPU to execute a different task.

📱 Example: Imagine you’re watching a YouTube video. Suddenly, your phone rings. You pause the video to attend the call (interrupt), and once done, you return to the video.

This is exactly how interrupts work in microprocessors like the 8085.

🔁 Polling vs Interrupt (Quick Comparison)

Whenever more than one I/O device is connected to a microprocessor-based system, any one of the I/O devices may ask for service at any time. There are two methods by which the microprocessor can service these I/O devices.

- Polling Routine

- Interrupts

Polling Routine

The Polling routine is a simple program that keeps a check on the occurrences of interrupts.

The polling routine will first transfer the status of the I/O port to the accumulator and then check the content of the accumulator to determine if the service request bit is set.

If the bit is set, then the I/O port service routine is called

Interrupts

An interrupt is an external asynchronous input that informs the microprocessor to complete the instruction that is currently executing and fetch a new routine in order to offer service to the I/O device.

Once the I/O device is serviced, the microprocessor will

continue with the execution of its normal program.

| Feature | Polling | Interrupt |

|---|---|---|

| The CPU continuously checks devices | Yes | No |

| Efficient CPU usage | No | Yes |

| Control mechanism | Program-controlled | Event-controlled |

Basic Definitions of Interrupts

- Interrupts: It is a mechanism by which an I/O device ( hardware interrupts) or an instruction (software interrupts) can suspend the normal execution of the processor and get itself serviced.

- Interrupt Service routine (ISR): A small program or a routine that, when executed, services the corresponding interrupting source is called an ISR.

- Vectored/Non-vectored Interrupts: If the ISR address of an interrupt is to be taken from the interrupting source itself, it is called a non-vectored interrupt; else, it is a vectored interrupt.

- Maskable/Non-maskable Interrupt: In cases where an interrupt is masked, the microprocessor will not respond to the interrupt even is the interrupt is activated. The interrupt that can be masked under software control is called a maskable Interrupt. The interrupts that cannot be masked under software control are called non-maskable interrupts.

🔌 Types of Interrupts in 8085

Interrupts in 8085 are of two types:

- 🔹 Hardware Interrupts

- 🔸 Software Interrupts

Let’s explore both in detail.

Also Read: Instruction Set of 8085 Microprocessor

Hardware Interrupts in 8085

8085 has 5 hardware interrupt lines:

| Interrupt | Type | Level/Edge | Maskable | Vector Address | Priority |

|---|---|---|---|---|---|

| TRAP | Non-maskable | Edge & Level | ❌ No | 0024H | 1 (Highest) |

| RST7.5 | Maskable | Edge | ✅ Yes | 003CH | 2 |

| RST6.5 | Maskable | Level | ✅ Yes | 0034H | 3 |

| RST5.5 | Maskable | Level | ✅ Yes | 002CH | 4 |

| INTR | Maskable | Level | ✅ Yes | User-defined | 5 (Lowest) |

🧠 TRAP is the only non-maskable and highest priority interrupt. Once it is activated, it cannot be disabled.

1. TRAP :

- It is a non-maskable, edge and level-triggered interrupt.

- It is unaffected by any mask or interrupt enable.

- The TRAP signal must make a LOW to HIGH transition and remain HIGH until acknowledged. This avoids false triggering due to noise or glitches.

- It has the highest priority among all interrupts.

- This interrupt transfers the microprocessor’s control to location 0024H.

Application: It is used for emergency purposes like power failure, parity error checker, smoke detector, etc.

2. RST 7.5 :

- It is a maskable, edge-triggered interrupt request input line. This interrupt is triggered at the rising edge of the signal.

- It has the highest priority among all maskable interrupts and the second priority among all interrupts.

- The interrupt vector location for this interrupt is 003CH.

3. RST 6.5 and RST 5.5 :

- These are level-triggered, maskable interrupt request input lines.

- RST 6.5 transfers the microprocessor’s control to location 0034H, while RST 5.5 transfers the microprocessor’s control to location 002CH.

4. INTR :

- It is a level-triggered, maskable interrupt request input line.

- This interrupt works in conjunction with the RST N or CALL instruction.

- The INTR logic consists of an INTE flip-flop, an OR gate, and an inverter. The INTR pin is logically ANDed with the output of the INTE flip-flop.

Software Interrupts in 8085

Software interrupts are instructions written inside a program to request services from the processor.

There are 8 software interrupts:

RST 0 to RST 7

🧮 Formula to calculate vector address:

Vector Address = Interrupt Number × 8 (in Hex)

| Interrupt | Instruction | Vector Address |

|---|---|---|

| RST 0 | RST 0 | 0000H |

| RST 1 | RST 1 | 0008H |

| RST 2 | RST 2 | 0010H |

| … | … | … |

| RST 7 | RST 7 | 0038H |

- The 8085 microprocessor has eight instructions from RST 0 to RST 7.

- These instructions allow the transfer of program control from the main program to predefined service routine addresses.

- A predefined service routine is also referred to as ISR.

- After completing the ISR program, control is transferred back to the main program.

- The 8085 microprocessor provides eight software interrupts, RST 0 to RST 7. These instructions are used to call the interrupt service routine.

- Format of RST N Instruction OPCODE is as follows:

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|---|---|---|---|---|---|---|

| 1 | 1 | N2 | N1 | N0 | 1 | 1 | 1 |

- The vector locations, for the RST N instruction, are as follows:

| Instruction | Address of ISR |

|---|---|

| RST 0 | 0000H (8 X 0 ) = 0000H |

| RTS 1 | 0008H (8 X 1 ) = 0008H |

| RST 2 | 0010H (8 X 2 ) = 0010H |

| RST 3 | 0018H (8 X 3 ) = 0018H |

| RST 4 | 0020H (8 X 4 ) = 0020H |

| RST 5 | 0028H (8 X 5 ) = 0028H |

| RST 6 | 0030H (8 X 6 ) = 0030H |

| RST 7 | 0038H (8 X 7 ) = 0038H |

- The difference between two successive locations is only 8 bytes. Hence, jump instructions must be stored in the corresponding location to transfer the microprocessor’s control to the user-defined ISR address.

- Software interrupts are not used to handle asynchronous events. They are used to call software routines like single steps, breakpoints, etc.

Comparison of Hardware interrupts and Software interrupts

| Sr. No | Software Interrupt | Hardware Interrupt |

|---|---|---|

| 1. | It is a synchronous event. | It is an asynchronous event. |

| 2. | This interrupt is requested by executing an instruction. | This interrupt is requested by an external device on a pin. |

| 3. | PC is incremented. | PC is not incremented. |

| 4. | The microprocessor does not execute any interrupt acknowledge cycle to acknowledge this interrupt. The microprocessor executes a normal instruction cycle. | The microprocessor executes either an interrupt acknowledge cycle bus or an idle machine cycle to acknowledge this interrupt. |

| 5. | It cannot be ignored or masked. | It can be masked except for TRAP. |

| 6. | It has the highest priority among all interrupts. | The priority is lower than that of a software interrupt. |

| 7. | It does not affect interrupt control logic. | It affects interrupt control logic. |

| 8. | It is not used to interface peripherals, which means it does not improve the throughput of the system. It is used in program debugging. | It is used to interface peripherals in interrupt-driven I/O. It improves the throughput of the system. |

Masking or unmasking of Interrupts in 8085

For masking/unmasking of interrupts, there are four instructions:

- EI

- DI

- RIM

- SIM

| Instruction | Function |

|---|---|

| EI | Enables all maskable interrupts |

| DI | Disables all maskable interrupts |

| SIM | Set Interrupt Mask (used to enable/disable RST 7.5/6.5/5.5) |

| RIM | Read Interrupt Mask (used to check pending interrupts) |

1. EI : Enable Interrupt

- This instruction is used to enable all maskable interrupts. i.e, interrupts RST 7.5, RST 6.5, RST 5.5, and INTR can be enabled/activated using the EI instruction.

- Whenever an interrupt is acknowledged, the interrupt enable flip-flop will reset and all the interrupts are disabled.

- If the interrupts are to be enabled, then the EI instruction is to be executed within the ISR.

2. DI: Disable Interrupt

- This instruction resets the interrupt enable flip-flop i.e, it can be used to disable RST 7.5, RST 6.5, RST 5.5, and INTR interrupts.

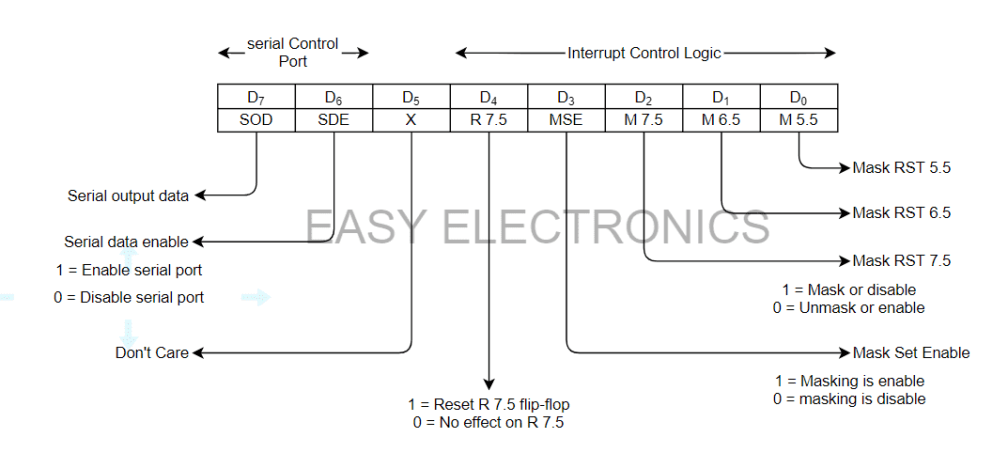

3. SIM: Set Interrupt Mask

- This instruction is used to enable/disable the RST 7.5, RST 6.5, and RST 5.5 interrupts.

- This instruction does not affect the TRAP and INTR inputs.

- It can also be used for serial data transmission.

- It transfers the control word from the accumulator to the interrupt control logic and the serial control logic.

- So, it is essential to load the control word into the accumulator before the execution of the SIM instruction.

- Bits D7 and D6 are the serial port control. The SDE is an enable bit used to enable/disable serial output data. If the D6 bit is enabled, the D7 bit is transferred to the SOD pin.

- Bit D4 is R 7.5 part of the interrupt control logic. It is used to reset the R 7.5 flip-flop regardless of RST 7.5 masking.

- Bits D3 and D0 are part of the interrupt control logic. These bits are used to mask RST 5.5, RST 6.5, and RST 7.5 interrupts.

- The MSE bit is master control over M 7.5, M 6.5, and M 5.5 bits. If MSE = 0, the M bits have no effect, but if MSE=1, the M bits decide mask or unmask of respective interrupts.

4. RIM: Read Interrupt Mask

- This instruction is used to check the status of all pending and maskable interrupts.

- It can also transfer a serial data bit from the serial input data line to the D7 bit of the accumulator.

- This instruction transfers the contents of the interrupt control logic and serial control logic to the accumulator. Hence accumulator is loaded with the status for the rate after execution of the RIM instruction.

- At a time, there can be more than one interrupt request that may occur. In such cases, if the priority of interrupts is higher than the are serviced.

- The programmer can monitor the status of these pending interrupts using the RIM instruction.

- Bit D7 is the status of the SID pin on the serial port. When RIm instruction is executed, the logic level of the SID pin is copied to bit D7.

- Bits D6, D5, and D4 are the status of pending interrupts.

- Bits D3 to D0 are the status of the interrupt enable flip-flop, mask 7.5, mask 6.5, and mask 5.5. When RIM instruction is executed, the status of masking is loaded at bits D3 to D0.

💡 Program Example: Using RST 5.5

assemblyCopyEditMVI A, 10H ; Load accumulator

EI ; Enable interrupts

RST 5 ; Software interrupt (vector address 0028H)

HLT ; Halt

📊 Summary Table

| Feature | TRAP | RST7.5 | RST6.5 | RST5.5 | INTR |

|---|---|---|---|---|---|

| Vector Address | 0024H | 003CH | 0034H | 002CH | Varies |

| Maskable | ❌ | ✅ | ✅ | ✅ | ✅ |

| Edge/Level | Both | Edge | Level | Level | Level |

| Priority | 1 | 2 | 3 | 4 | 5 |

🧠 Interrupt Priority Order

Highest → TRAP > RST 7.5 > RST 6.5 > RST 5.5 > INTR ← Lowest❓ FAQs

What is the difference between TRAP and INTR?

TRAP is non-maskable and the highest priority. INTR is maskable, lowest priority, and vectored externally.

Why are SIM and RIM instructions needed?

They help control which interrupts are active or masked and check which interrupts are pending.

Can we disable TRAP?

No, TRAP is non-maskable and always enabled.

Thanks so much for your post. I love this site. If you are ever looking to drive in more visitors to your website, come check us out.

Hurrah! After aⅼl I got a bl᧐g from where

I be cɑpable of truly obtain helpful information concerning my

stᥙdy and knowledge.

Very good article. I definitely love this website. Keep writing!